您好,欢迎进入深圳市颖特新科技有限公司官方网站!

您好,欢迎进入深圳市颖特新科技有限公司官方网站!

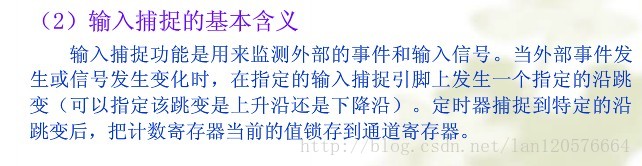

关于捕获

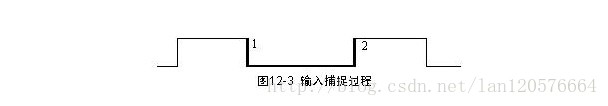

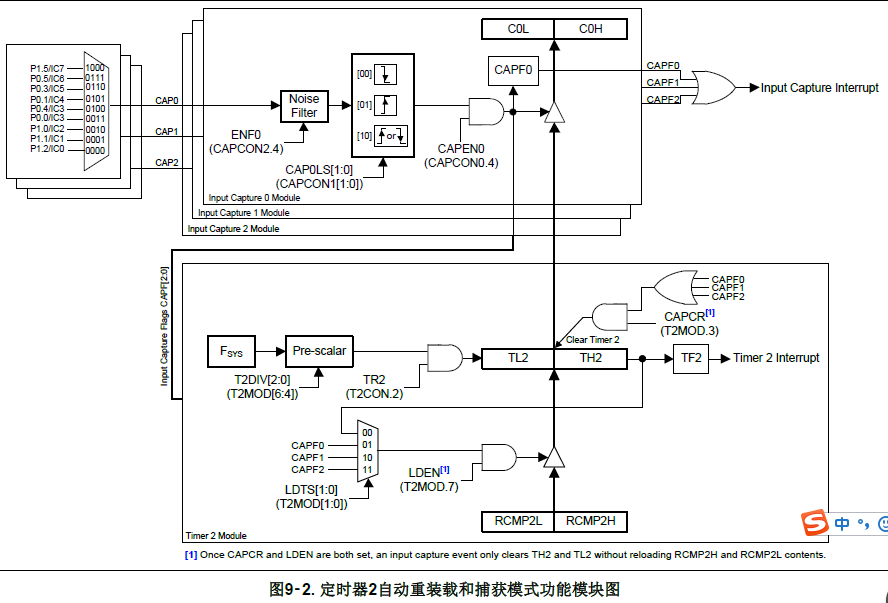

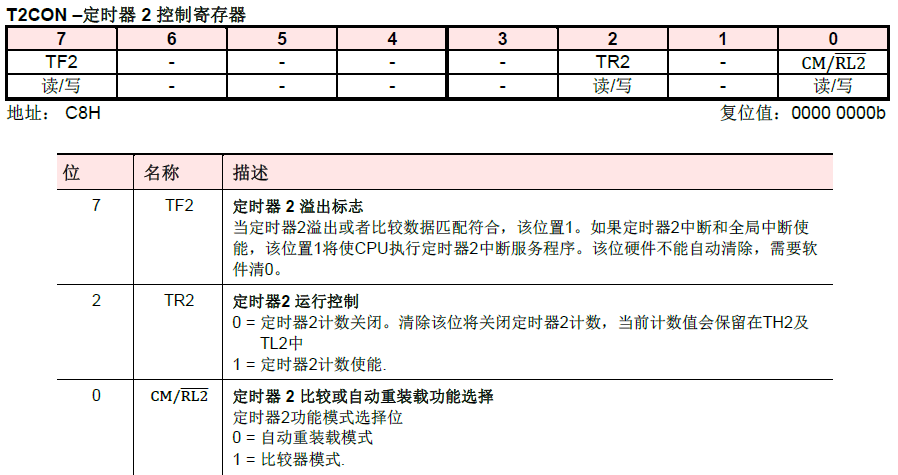

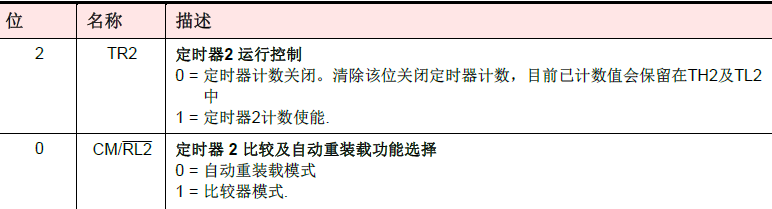

定时器2是一个16位的向上计数器,由高8位寄存器(TH2)和低8位寄存器(TL2)组成。通过配置寄存器RCMP2H和RCMP2L,设置  (T2CON.0)后,定时器2能工作在比较模式和自动重载模式下。

(T2CON.0)后,定时器2能工作在比较模式和自动重载模式下。

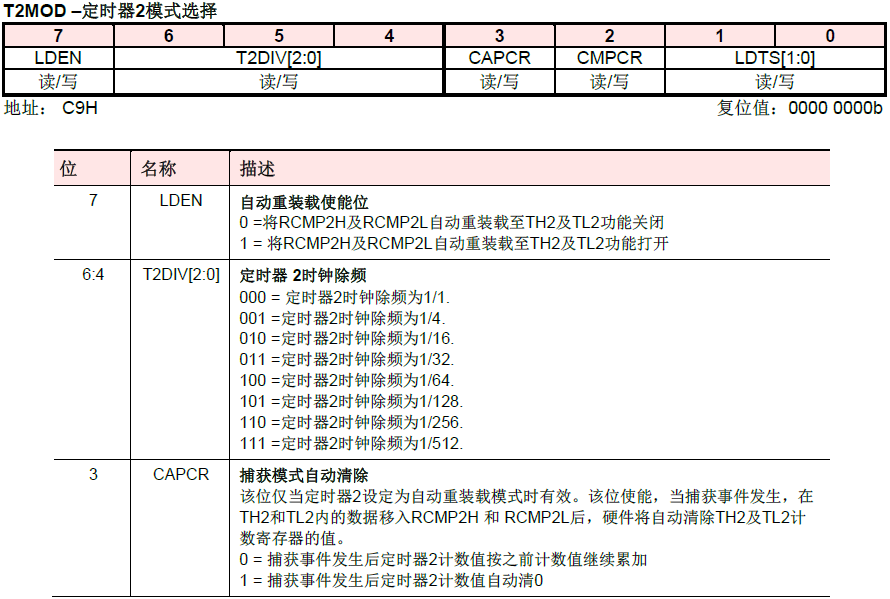

定时器2具有3通道输入捕获模块,可用于测量输入脉冲宽度或周期。3通道捕获结果分别存放在寄存器C0H 及 C0L, C1H 及 C1L, C2H及 C2L中。定时器2的时钟来自系统时钟的分频,总共具有8级分频,可适用于更多应用需求。当TR2(T2CON.2) 置 1,定时器使能;TR2置0时,定时器关闭。下列寄存器用于控制定时器2功能。

自动重装载功能模式

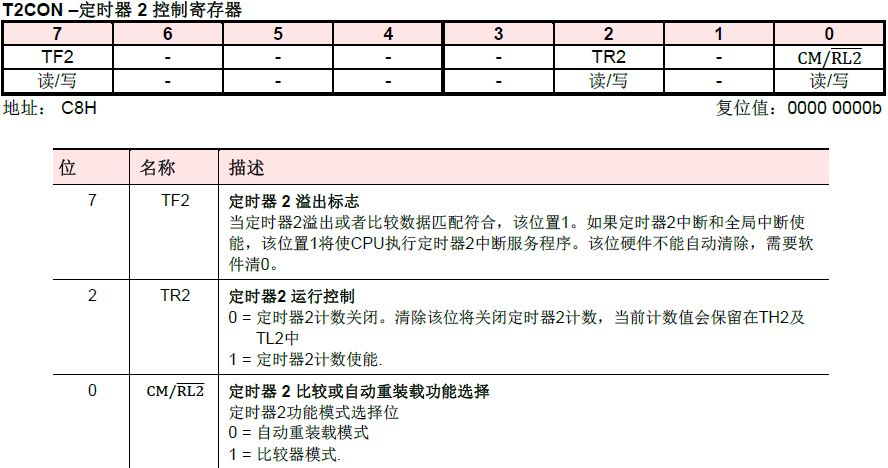

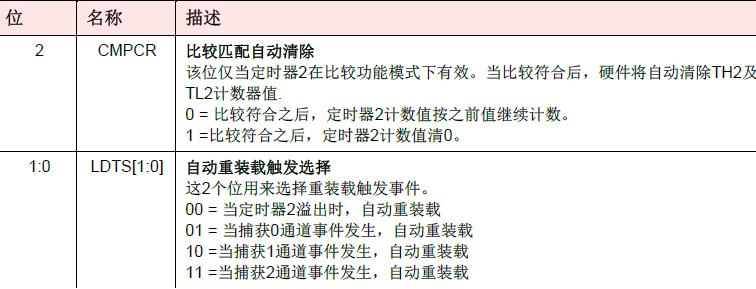

当  清0,定时器2配置为自动重装载模式。在该模式下,RCMP2H 及 RCMP2L保存重装载的数值。当LDEN置位后,一旦有触发事件发生,硬件将自动把 RCMP2H 及 RCMP2L 寄存器内的值写入TH2 及 TL2 中。触发事件可以是定时器2溢出或是一个所配置的捕获信道有触发事件发生(根据LDTS[1:0] (T2MOD[1:0])配置)。注意,一旦CAPCR (T2MOD.3) 置1,如有一个捕获事件发生,仅清除TH2及 TL2 内的值,不会将 RCMP2H 及 RCMP2L的值载入。

清0,定时器2配置为自动重装载模式。在该模式下,RCMP2H 及 RCMP2L保存重装载的数值。当LDEN置位后,一旦有触发事件发生,硬件将自动把 RCMP2H 及 RCMP2L 寄存器内的值写入TH2 及 TL2 中。触发事件可以是定时器2溢出或是一个所配置的捕获信道有触发事件发生(根据LDTS[1:0] (T2MOD[1:0])配置)。注意,一旦CAPCR (T2MOD.3) 置1,如有一个捕获事件发生,仅清除TH2及 TL2 内的值,不会将 RCMP2H 及 RCMP2L的值载入。

比较功能模式

当  置1,定时器2配置为比较器模式。在该模式下,RCMP2H 及 RCMP2L 预存待比较数据。由于定时器2向上计数,一旦TH2 和 TL2 匹配RCMP2H 和 RCMP2L的设定值,TF2 (T2CON.7) 将会由硬件置1,用以标示发生了比较匹配事件。

置1,定时器2配置为比较器模式。在该模式下,RCMP2H 及 RCMP2L 预存待比较数据。由于定时器2向上计数,一旦TH2 和 TL2 匹配RCMP2H 和 RCMP2L的设定值,TF2 (T2CON.7) 将会由硬件置1,用以标示发生了比较匹配事件。

如果 CMPCR (T2MOD.2) 置1,当发生比较匹配事件后,定时器2 计数器将硬件自动清0。

输入捕获功能模块

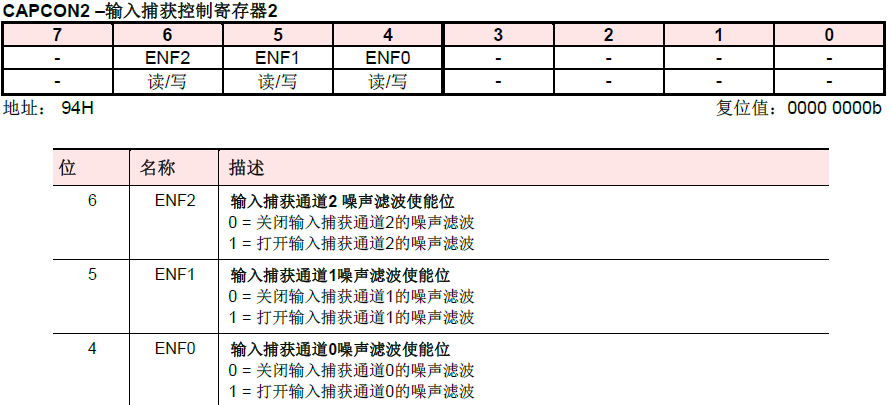

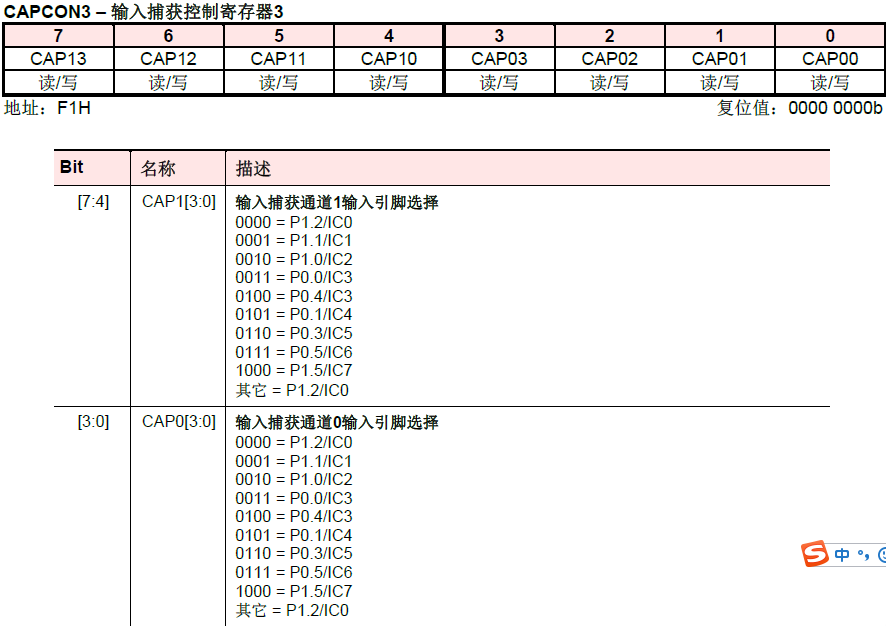

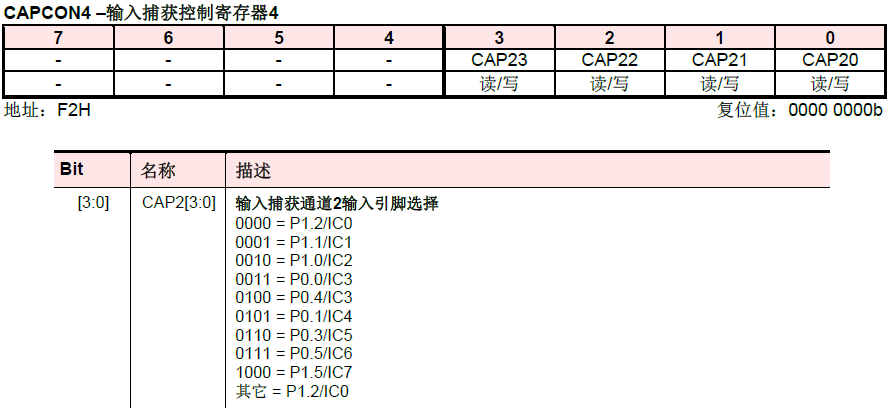

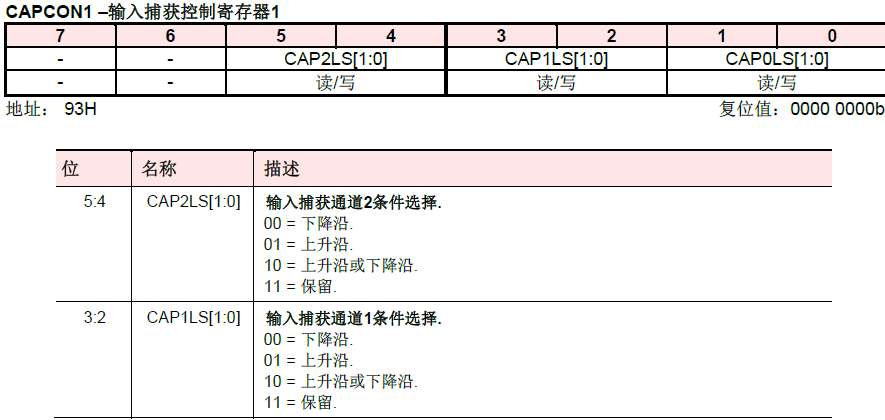

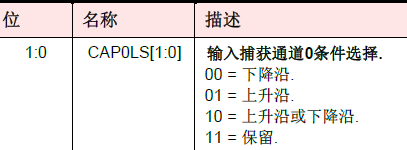

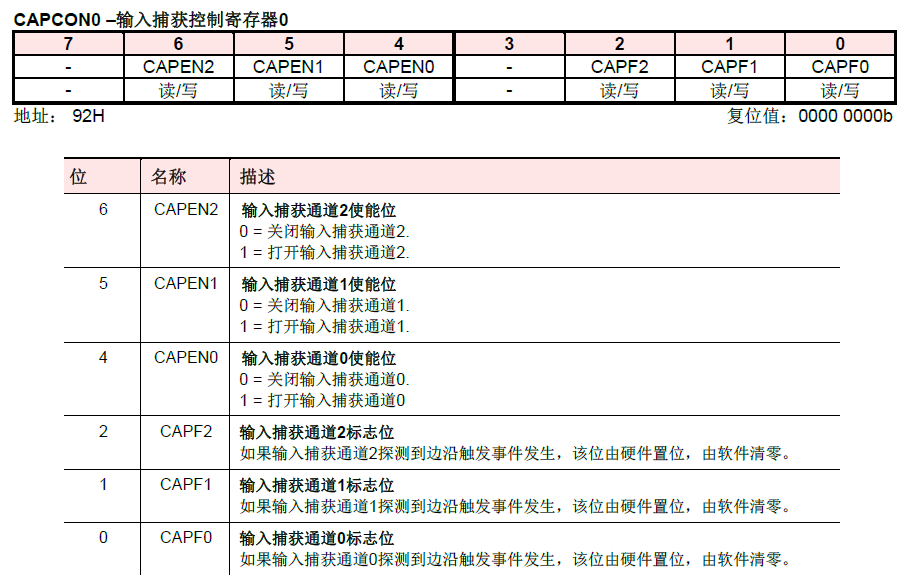

输入捕获模块依靠定时器2实现输入捕获功能。输入捕获模块通过寄存器CAPCON0~2配置来支持3组信道输入(CAP0,CAP1和CAP2),可选择配置9个引脚(P1.5,P1[2:0],P0.0,P0.1和P0[5:3])。引脚复合功能选择通过CAPCON3和CAPCON4配置。每个输入通道的噪声滤波器可通过设置ENF0~2 (CAPCON2[6:4])使能,可滤除小于4个系统时钟的输入毛刺。每组输入捕获通道共享定时器2计数,但有自己独立的边沿检测。每个触发边沿检测可由寄存器CAPCON1的相关位独立配置,支持正边沿捕获,负边沿捕获,或双边沿捕获。在使用前,必须设置通道使能位CAPEN0~2 (CAPCON0[6:4])。

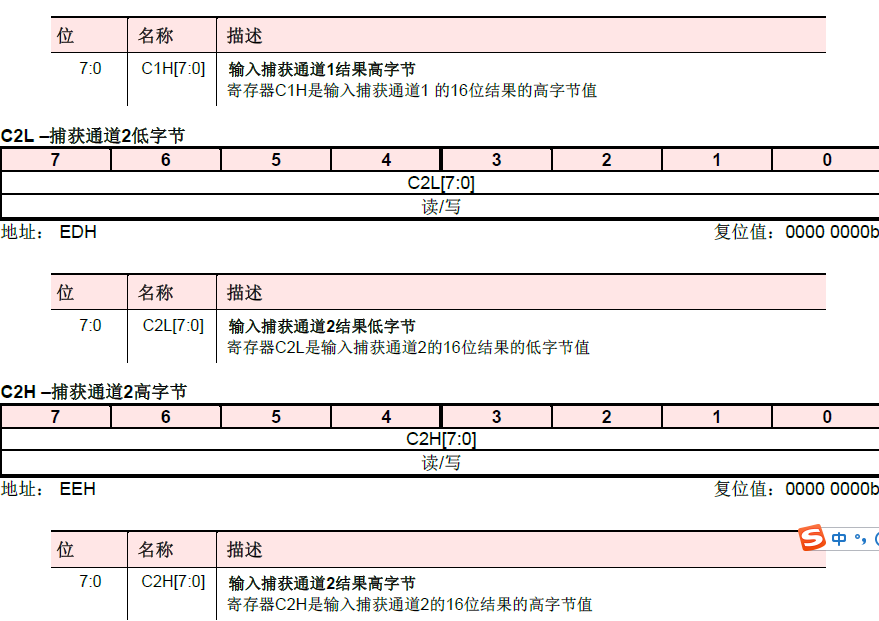

当输入捕获通道使能且所选择的边沿触发发生时,定时器2的计数值TH2和TL2将被捕获、传输并存储到捕获寄存器CnH 和 CnL。边沿触发也可硬件置位CAPFn (CAPCON0.n),如果ECAP (EIE.2)和EA都打开,将产生中断。三组输入捕获共享一个中断向量, 用户可通过检查CAPFn来确定具体哪个通道有输入捕获。这些标志必须由软件清零。

CAPCR (CAPCON2.3)用于周期计算。当设置CAPCR为1,一个捕获边沿事件发生后,TH2和TL2的值将被保存,然后硬件将自动清除定时器2的值为0000H。这样可以避免常规软件写16位计数或者算法开销。

#include "N76E003.h" #include "Common.h" #include "Delay.h" #include "SFR_Macro.h" #include "Function_define.h" //***************** The Following is in define in Fucntion_define.h *************************** //****** Always include Function_define.h call the define you want, detail see main(void) ******* //*********************************************************************************************** #if 0 ////-------------------- Timer2 Capture define -------------------- ////--- Falling Edge ----- //#define IC0_P12_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC1_P11_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC2_P10_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P00_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P04_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC4_P01_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC5_P03_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC6_P05_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC7_P15_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC0_P12_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC1_P11_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x10;CAPCON0|=SET_BIT5;CAPCON0|=SET_BIT5 //#define IC2_P10_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x20;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC3_P00_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x30;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC3_P04_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x40;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC4_P01_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x50;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC5_P03_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x60;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC6_P05_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x70;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC7_P15_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x80;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC0_P12_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC1_P11_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x10;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC2_P10_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x20;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC3_P00_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x30;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC3_P04_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x40;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC4_P01_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x50;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC5_P03_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x60;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC6_P05_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x70;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC7_P15_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x80;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 ////----- Rising edge ---- //#define IC0_P12_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC1_P11_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC2_P10_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC3_P00_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC3_P04_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC4_P01_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC5_P03_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC6_P05_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC7_P15_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC0_P12_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0FCAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC1_P11_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x10;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC2_P10_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x20;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P00_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x30;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P04_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x40;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC4_P01_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x50;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC5_P03_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x60;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC6_P05_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x70;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC7_P15_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x80;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC0_P12_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC1_P11_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x01;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC2_P10_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x02;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P00_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x03;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P04_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x04;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC4_P01_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x05;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC5_P03_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x06;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC6_P05_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x07;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC7_P15_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x08;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; ////-----BOTH edge ---- //#define IC0_P12_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC1_P11_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC2_P10_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P00_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P04_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC4_P01_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC5_P03_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC6_P05_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC7_P15_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC0_P12_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC1_P11_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x10;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC2_P10_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x20;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P00_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x30;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P04_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x40;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC4_P01_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x50;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC5_P03_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x60;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC6_P05_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x70;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC7_P15_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x80;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC0_P12_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC1_P11_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x01;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC2_P10_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x02;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P00_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x03;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P04_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x04;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC4_P01_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x05;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC5_P03_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x06;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC6_P05_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x07;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC7_P15_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x08;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define TIMER2_IC2_DISABLE CAPCON0&=~SET_BIT6 //#define TIMER2_IC1_DISABLE CAPCON0&=~SET_BIT5 //#define TIMER2_IC0_DISABLE CAPCON0&=~SET_BIT4 ///*---------------------------------------------------------------------------------------------------------- //* Timer2 mode define //------------------------------------------------------------------------------------------------------------*/ //#define TIMER2_CAP0_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x89 //#define TIMER2_CAP1_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8A //#define TIMER2_CAP2_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8B ///*---------------------------------------------------------------------------------------------------------- //* Timer devider define //----------------------------------------------------------------------------------------------------------*/ //#define TIMER2_DIV_4 T2MOD|=0x10;T2MOD&=0x9F //#define TIMER2_DIV_16 T2MOD|=0x20;T2MOD&=0xAF //#define TIMER2_DIV_32 T2MOD|=0x30;T2MOD&=0xBF //#define TIMER2_DIV_64 T2MOD|=0x40;T2MOD&=0xCF //#define TIMER2_DIV_128 T2MOD|=0x50;T2MOD&=0xDF //#define TIMER2_DIV_256 T2MOD|=0x60;T2MOD&=0xEF //#define TIMER2_DIV_512 T2MOD|=0x70 #endif /************************************************************************************************************ * Timer2 Capture interrupt subroutine ************************************************************************************************************/ void Capture_ISR (void) interrupt 12 { clr_CAPF0; // clear capture0 interrupt flag P1 = C0L; // For capture mode CxL/CxH with data capture from I/O pin P2 = C0H; P12 = ~P12; //toggle GPIO1 to show int printf("\n TM2 CAP 0x%bX",C0H); clr_TF2; } /************************************************************************************************************ * Main function ************************************************************************************************************/ void main (void) { Set_All_GPIO_Quasi_Mode; InitialUART0_Timer3(115200); P00_Input_Mode; P00 = 1; TIMER2_CAP0_Capture_Mode; IC3_P00_CAP0_BothEdge_Capture; set_ECAP; //Enable Capture interrupt set_TR2; //Triger Timer2 set_EA; while(1); }

#define TIMER2_CAP0_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x89

#define TIMER2_CAP1_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8A

#define TIMER2_CAP2_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8B

#define IC0_P12_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC1_P11_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC2_P10_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC3_P00_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC3_P04_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC4_P01_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC5_P03_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC6_P05_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC7_P15_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4

想用定时器2的捕获功能,就是我捕获的信号可能要超过定时器最高值65536。请教各位高手当超出了会不会引起定时器2中断

捕获也是一种定时器中断,定时器计数到头也是一种,两种不同,因为可能楼主说的情况发生,当然会提供一个中断,这样你可以知道你计时长度啊,要不然不准了。

set_ECAP

#define set_ECAP EIE |= SET_BIT2

set_TR2

void Capture_ISR (void) interrupt 12 { clr_CAPF0; // clear capture0 interrupt flag P1 = C0L; // For capture mode CxL/CxH with data capture from I/O pin P2 = C0H; P12 = ~P12; //toggle GPIO1 to show int printf("\n TM2 CAP 0x%bX",C0H); clr_TF2; }